电路描述语言,先设计电路后写程序。

端口列表有输入输出类型(input、output、inout),数据信号类型(wire,reg),信号位宽

output reg [3:0] S

若声明4'b100则左补零为0100

&4'0100从左到右自己做与运算,结果只有一位

>>>算数右移,补符号位

assign 为连续赋值语句,只要输入改变,输出立刻计算,赋值目标必须是wire类型。

always为过程赋值语句,只当条件触发时执行,其余时间挂起。赋值目标必须是reg类型,条件分为边缘敏感和电平敏感:

always @(posedge clk)

always @(negedge clk)

always @(a,b,c) always @(a or b or c)

区别:

// 只有当clk上升沿到来时才将D赋值给Q

always @(posedge clk) begin

Q=D

end

// 只要D变化就将D赋值给Q

always @(Q) begin

Q=D

end

always语句顺序执行,其他的语句并行执行。

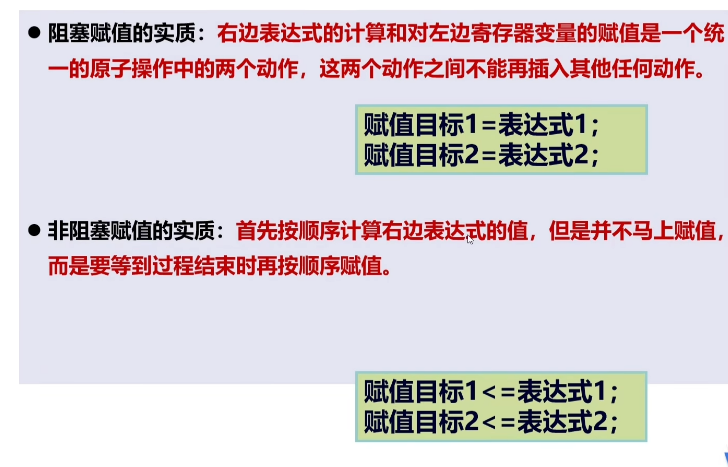

阻塞赋值和非阻塞赋值:

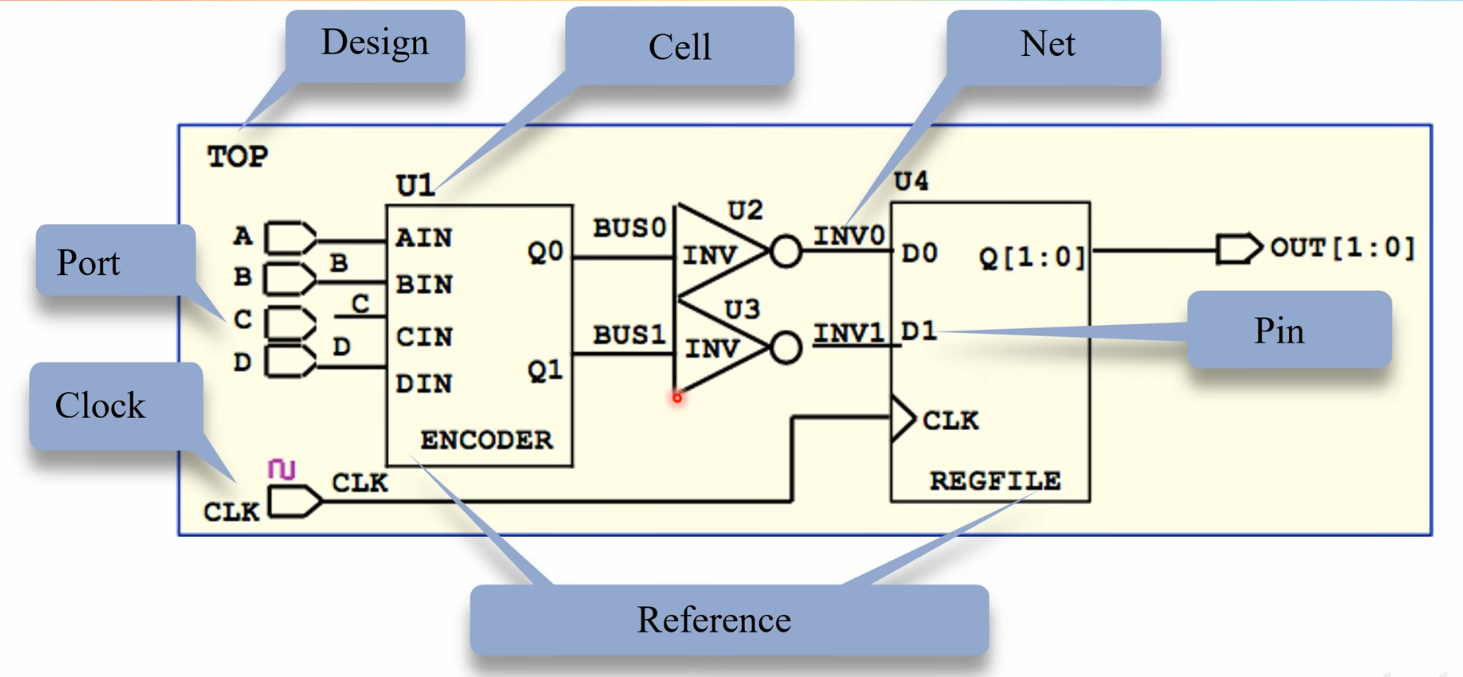

并发执行逻辑: